偶爾一次用PADS2007的原理圖與PCB同步時遇到以下問題:引號內為錯誤報告

“* Because the current design is in default layer mode and the decal is in increased layer mode, you cannot add decal “xxx”. Open Layer Setup dialog box and change the layer mode of the design to increased layers.”

資訊提示意思為,有一個器件導入不成功。”

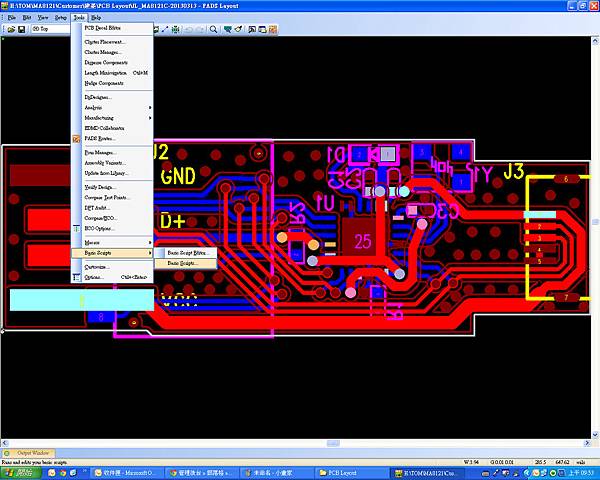

按照提示將Layer mode 進行修改,把當前PADS Layout的設計檔的層設置也設置成增強模式即可,具體操作:setup->layer definition->clik max layers tab。問題解決,但是新的問題又來了。PCB檔的層數都變成200多層了,看著實在不爽,那麼有沒有辦法不增加層數來處理呢?

動物愛心

動物愛心