PMOS 和 NMOS 作為開關時的真值表,主要取決於 閘極電壓 (Vg) 與 源極電壓 (Vs) 的關係,來判斷導通或截止。以下是最常見的情況(假設源極接 VDD 或 GND,體接源極):

✅ NMOS 開關

NMOS 導通條件:

Vgs=Vg−Vs≥VthV_{gs} = V_g - V_s \ge V_{th} (通常 Vth ≈ 0.7V)

-

源極 Vs ≈ GND (0V),閘極電壓 Vg 高電位時導通。

| Vg | 狀態 |

|---|---|

| 0 | OFF(截止) |

| 1 | ON(導通) |

結論:NMOS 需要高電位(邏輯 1)打開。

✅ PMOS 開關

PMOS 導通條件:

Vsg=Vs−Vg≥∣Vth∣V_{sg} = V_s - V_g \ge |V_{th}|

-

源極 Vs ≈ VDD (1),閘極電壓 Vg 低電位時導通。

| Vg | 狀態 |

|---|---|

| 0 | ON(導通) |

| 1 | OFF(截止) |

結論:PMOS 需要低電位(邏輯 0)打開。

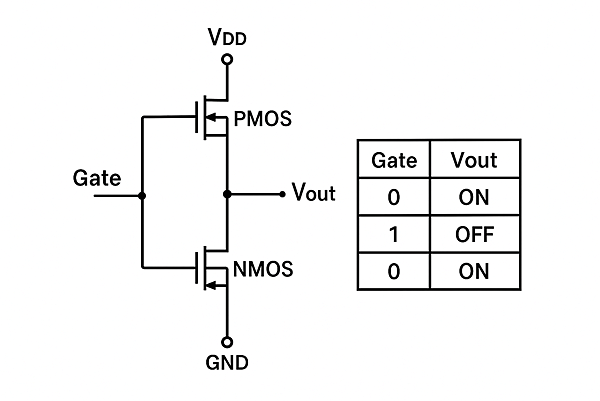

✅ 總結真值表(假設 VDD=1,GND=0)

| 開關類型 | Gate=0 | Gate=1 |

|---|---|---|

| NMOS | OFF | ON |

| PMOS | ON | OFF |

請先 登入 以發表留言。